Transistorutveckling: från plan till CFET, 3D-integration omdefinierar halvledarframsteg

I mer än ett halvt sekel växte halvledarindustrin genom att följa en enkel regel: gör transistorer mindre.Krympande funktionsstorlekar gav högre prestanda, lägre effekt och lägre kostnad per transistor.Men idag har denna väg nått sin fysiska och ekonomiska gräns.Eran av ren skalning är över, och en ny era av strukturell innovation och 3D-integration har börjat.

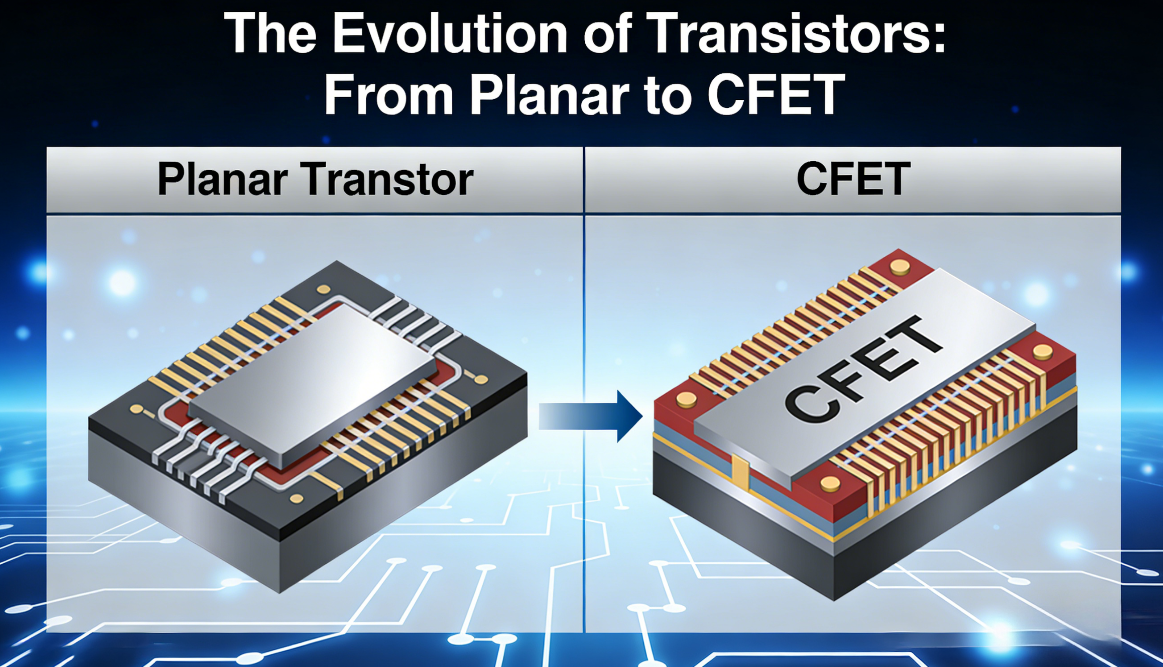

Själva transistorn genomgår en fullständig arkitektonisk revolution.Från plan MOSFET till FinFET, från GAA nanosheet till CFET-stapling, representerar varje steg en förskjutning från att krympa till bygga om transistorn i tre dimensioner.Detta är inte bara stegvis förbättring – det är en fullständig omdefiniering av hur chips levererar prestanda.

De fyra generationerna av transistorarkitektur

1. Plan transistor (traditionell 2D)

Den klassiska platta strukturen, där grinden styr kanalen uppifrån.Det dominerade från de första dagarna ner till 40nm och 28nm.När dimensionerna krympte ytterligare blev läckström och elektrostatisk kontroll olösliga problem.

2. FinFET (3D Gate Control)

Kanalen blir en vertikal "fena", där grinden lindas runt tre sidor.Detta förbättrar drastiskt den elektrostatiska kontrollen, minskar läckage och möjliggör nedskalning till 7nm, 5nm och till och med 3nm.FinFET blev grunden för den moderna högpresterande chip-eran.

3. GAA Nanosheet (Gate-All-Around)

Vid 2nm och lägre når FinFET sin gräns.GAA ersätter fenan med staplade horisontella nanotrådar eller ark, helt omgivna av grinden.Den ger bättre kontroll, lägre effekt och högre drivström.GAA är nu den vanliga strukturen för 2nm-klasschips över TSMC, Samsung och Intel.

4. CFET (komplementär FET)

Nästa gräns: att stapla NMOS och PMOS vertikalt.CFET packar två transistorer i fotavtrycket av en, vilket drastiskt minskar arean och förbättrar densiteten.Det är det ultimata evolutionära slutet av transistorskalning innan äkta 3D-systemintegration tar över.

Varför ensam skalning inte längre fungerar

- Processkostnaderna stiger exponentiellt vid varje ny nod

- Kvantläckage och fysiska begränsningar hårdnar gränserna

- Sammankopplingsfördröjning och strömförbrukning går om transistorhastigheten

- Stora monolitiska spån lider av lågt utbyte och höga kostnader

Branschen har insett: prestanda kommer inte längre från mindre transistorer.Det kommer från bättre anslutningar, smartare arkitektur och vertikal integration.

The New Era: Tre lager av 3D-innovation

Halvledarutvecklingen definieras nu av tre dimensioner av 3D-design:

- 3D-transistor: FinFET, GAA, CFET – bygger transistorn vertikalt

- Stapling av 3D-enheter: Minne på logik, hybridbindning, SRAM-stapling

- 3D-systemintegration: Chiplet, 2,5D/3D-förpackning, interposer-baserad integration

Tillsammans bildar de 3D×3D×3D era: transistorn, enheten och systemet blir alla tredimensionella.

DTCO: Den nya kärnkompetensen

När skalningen slutar, Design Technology Co-Optimization (DTCO) blir kritisk.Det innebär att samdesigna arkitektur, transistorstruktur, metallrouting och förpackning från början.De starkaste företagen är inte längre bara processledare – de är integratörer på systemnivå.

Ledningseffektivitet, kraftleverans, termisk design och bandbreddstäthet avgör nu produktens verkliga prestanda.

AI är den ultimata drivkraften

AI och högpresterande datorer kräver oöverträffad bandbredd, energieffektivitet och densitet.Dessa krav kan inte uppfyllas med traditionell skalning.De kräver:

- Minnes-datorsammankoppling med ultrahög bandbredd

- Extrem energieffektivitet per operation

- Massiv parallellism och tät integration

AI har tvingat hela branschen att överge ren skalning och anamma fullständig heterogen 3D-integration.

Slutsats: Framtiden är inte mindre, den är högre

Åldern för krympande transistorer bleknar.Framtiden för halvledare handlar inte om att göra enheter mindre – det handlar om att bygga system högre, tätare och mer intelligent ansluten.

Från Planar till FinFET till GAA till CFET, transistorn har slutfört sin utveckling.Nästa strid kommer att utkämpas 3D-integration, avancerad paketering och design på systemnivå.Det är här som nästa decennium av halvledarledarskap kommer att avgöras.